Time: 3 Hour Final Exam

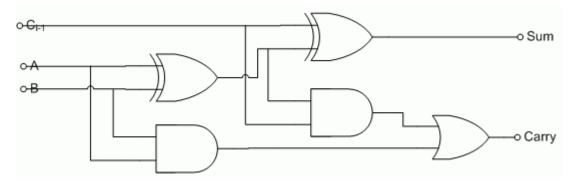

Q1/Design a full adder using two half adders and one OR Gate.

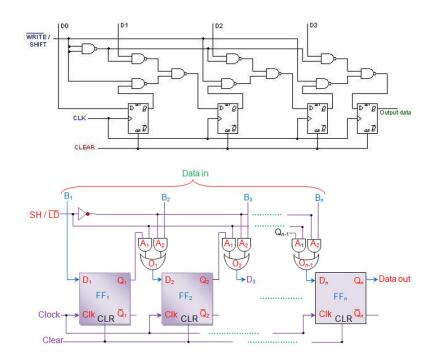

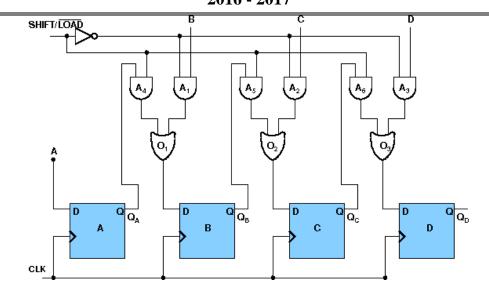

Q2/Design 4 bit PISO.

## Drawing any one of follow is correct

Time: 3 Hour Final Exam

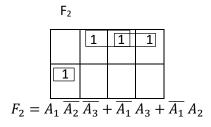

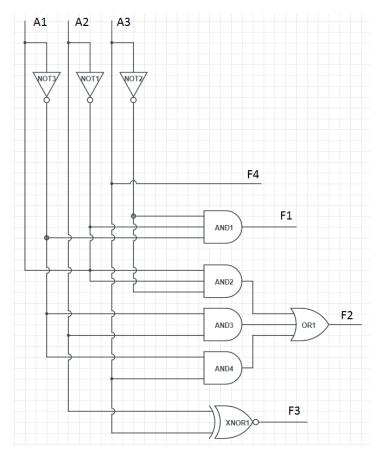

**Q3**/ Design a combinational circuit whose input is a 3-bit number and whose output is the 2's complement of the input number.

| $QA_1$ | A <sub>2</sub> | A <sub>3</sub> | F <sub>1</sub> | F <sub>2</sub> | F <sub>3</sub> | F <sub>4</sub> |

|--------|----------------|----------------|----------------|----------------|----------------|----------------|

| QA1    | 7-2            | Λ3             | '1             | 1 2            | 13             | 14             |

| 0      | 0              | 0              | 1              | 0              | 0              | 0              |

| 0      | 0              | 1              | 0              | 1              | 1              | 1              |

| 0      | 1              | 0              | 0              | 1              | 1              | 0              |

| 0      | 1              | 1              | 0              | 1              | 0              | 1              |

| 1      | 0              | 0              | 0              | 1              | 0              | 0              |

| 1      | 0              | 1              | 0              | 0              | 1              | 1              |

| 1      | 1              | 0              | 0              | 0              | 1              | 0              |

| 1      | 1              | 1              | 0              | 0              | 0              | 1              |

$F_1 = \overline{A_1} \, \overline{A_2} \, \overline{A_3}$

$F_1$

Time: 3 Hour Final Exam

$F_{3}$   $\boxed{1}$   $\boxed{1}$   $T_{3}$   $\boxed{1}$   $\boxed{1}$

$F_3=A_2{\displaystyle \bigoplus} A_3$

$F_4$   $\boxed{\begin{array}{c|c} 1 & 1 \\ \hline & 1 & 1 \\ \hline & 1 & 1 \\ \hline & F_4 = A_3 \\ \end{array}}$

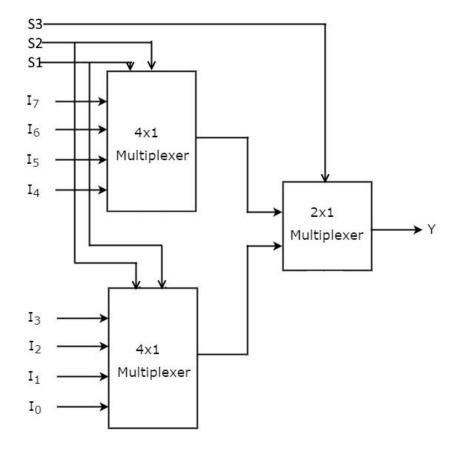

## **Q4**/Answer **ONE** branch only

A. Design 8 to 1 Multiplexer from 4 to 1 multiplexes and 2 to 1 Multiplexer.

Time: 3 Hour Final Exam

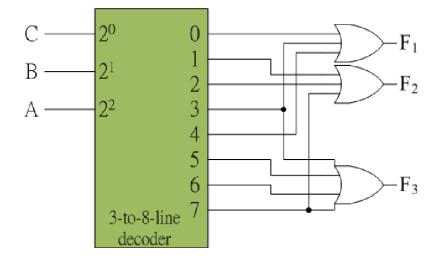

**Q5**/ A combinational circuit is defined by the following three Boolean functions

$$F_1(A, B, C) = \sum m(0,3,4)$$

$$F_2(A, B, C) = \sum m(1,2,7)$$

$$F_3(A, B, C) = \prod M(0,1,2,4)$$

Implement the circuit with a decoder and external OR gates.

Time: 3 Hour Final Exam

**Q6/**

1.

$$F(W, X, Y, Z) = \sum m(0,1,2,4,5,6,8,9,12,13,14)$$

2.

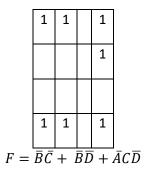

$$F = \overline{A}\overline{B}\overline{C} + \overline{B}C\overline{D} + A\overline{B}\overline{C} + \overline{A}BC\overline{D}$$

Time: 3 Hour Final Exam

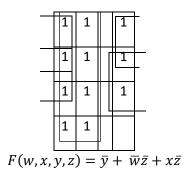

3.  $F(W, X, Y, Z) = \sum m(4,6,7,8,12,15), d(W, X, Y, Z) = \sum m(2,3,5,10,11,14)$

$$F(w, x, \overline{y, z}) = \overline{y} + x\overline{z} + w\overline{z}$$

$$F(w, x, y, z) = y + \overline{w}x + w\overline{z}$$

B- Simplify the Boolean Function F and implemented it with NAND and NOR gates

$$F = A\overline{C} + ACE + AC\overline{E} + \overline{A}C\overline{D} + \overline{A}\overline{D}\overline{E}$$